PCI-SIG 宣布利用全新 CopprLink 电缆设计开发下一代 PCIe Gen 5.0 和 Gen 6.0 标准。虽然 PCI-SIG 没有详细说明新 CopprLink 电缆的规格或设计变化,但它确认了命名方案。CopprLink 电缆将根据 PCIe Gen 5.0 和 Gen 6.0 硬件提供内部和外部解决方案。根据 PCI-SIG 的说法,外部和内部电缆规格目前正在制定中,目标是在今年内发布。以下是新闻稿全文:

PCI-SIG 在 SC23 大会上强调 PCIe 技术是高性能计算的首选互连技术,成员演示 PCIe 技术并宣布新的 PCI Express 电缆命名方案。

PCI-SIG 宣布 PCIe 内部和外部电缆的新命名方案为 CopprLink。PCIe 5.0 和 PCIe 6.0 内部和外部电缆规范目前正在开发中,预计将于 2024 年发布。

PCI-SIG是拥有和管理作为开放式行业标准的PCI规范的联盟,其成员将在SC23的1401号展位展示PCI Express (PCIe)技术演示。

PCI-SIG 邀请 SC23 参会者参观 1401 号展台,观看演示并进一步了解 PCIe 技术生态系统。演示将突出 PCIe 技术作为高性能计算 (HPC) 应用首选高速 I/O 互连技术的作用。参加演示的公司包括 Astera Labs、Dolphin Interconnect Solutions、Synopsys 和 Tektronix。

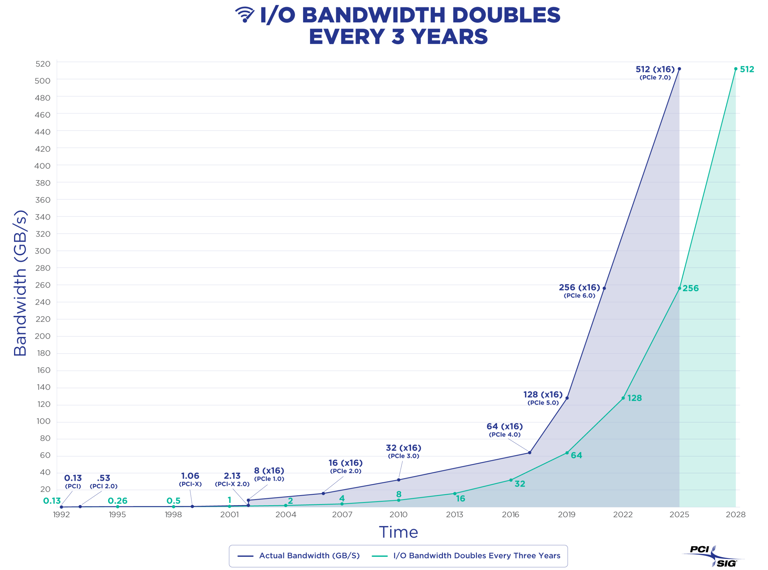

此次演示的重点是高性能计算应用,因此 CopprLink 应瞄准接口,我们可能会关注接口电缆而不是电源电缆,以便为下一代平台上的各种设备提供最佳传输带宽。PCIe 6.0 平台的传输速率将翻一番,从 32 GT/s(5.0 代)提高到 64 GT/s(6.0 代)。新标准还有望在 x16 通道链路上提供 256 GB/s 的带宽。

如果 CopprLink 与电源接口电缆有关,那么PCI-SIG将努力解决在设计当前 12VHPWR Gen 5.0 标准时遇到的一些问题。虽然随着 12V-2×6 标准的发布,设计逐渐得到优化,但似乎仍有改进的余地,尤其是考虑到未来的 PCIe Gen 6.0 硬件。期待在未来几个月内了解 CopprLink PCIe Gen 5.0 和 Gen 6.0 电缆的更多详情。

Linuxeden开源社区

Linuxeden开源社区